L2 Controller Board Rev.1, User Manual

Ref.: MST-CAM-UM-0227-DESY

Version: 10

Date: 22/07/2025

Page: 1/16

# L2 Controller Board Rev.1, User Manual

| Author             | Laboratory | Approved by | Laboratory |

|--------------------|------------|-------------|------------|

| Karl-Heinz Sulanke | DESY       |             |            |

|                    |            |             |            |

|                    |            |             |            |

|                    |            |             |            |

|      | List of Abbreviations              |      |                                    |  |  |

|------|------------------------------------|------|------------------------------------|--|--|

| SPI  | Serial Peripheral Interface        | RW   | Read / Write                       |  |  |

| L2CB | L2 Controller Board                | RO   | Read Only                          |  |  |

| CTDB | Clock & Trigger Distribution Board | RWC  | Read / Write Clear                 |  |  |

| L2BP | L2 Crate Backplane                 | 76h  | 76 hexadecimal                     |  |  |

| LVDS | Low Voltage Digital Signalling     | RTC  | Real Time Clock                    |  |  |

| TIB  | Trigger Interface Board            | MCU  | Microcontroller Unit               |  |  |

| PPS  | Pulse Per Second                   | LVDS | Low Voltage Differential Signaling |  |  |

| FEB  | Frontend Board                     | MCF  | Muon Candidate Flag                |  |  |

| L2BP | L2-crate Backplane                 | L1DT | L2-Trigger Dead Time               |  |  |

| L1A  | L1 trigger Accepted                |      |                                    |  |  |

L2 Controller Board Rev.1, User Manual

Ref.: MST-CAM-UM-0227-DESY

Version: 10

Date: 22/07/2025

Page: 2/16

|         | History    |        |                                                                                        |

|---------|------------|--------|----------------------------------------------------------------------------------------|

| Version | Date       | Firmw. | Observation                                                                            |

|         |            | Rev.   |                                                                                        |

| 1       | 18/10/2016 | 001    | Draft                                                                                  |

| 2       | 20/03/2017 | 002    |                                                                                        |

| 3       | 29/05/2018 | 005    |                                                                                        |

| 4       | 28/03/2023 | 008    |                                                                                        |

| 5       | 21/04/2023 | 008    | Muon trigger introduced                                                                |

| 6       | 01/03/2024 | 009    | Muon trigger delay register introduced                                                 |

| 7       | 11/09/2024 | 014    | Programmable (ctrl_rg(14)) L2 trigger gating if FEB-BUSY is on                         |

| 8       | 23/09/2024 | 016    | Programmable upgoing TIB trigger (L1or = TIB_CAMERA_Tx) dead time register L1DT added. |

|         |            |        | Programmable (ctrl_rg(13) Muon_Candidate_Flag-Enable added.                            |

|         |            |        | NOTE!!! To be compliant with the L2CB1 schematic, the                                  |

|         |            |        | naming has changed as follows: L1xxx are going up to the TIB,                          |

|         |            |        | while the downgoing trigger signals are L2xxx, send as L1A by                          |

|         |            |        | the DTB to the FEB finally.                                                            |

| 9       | 26/03/2025 | 021    | ctrl_rg(0) =TIB TRIG BUSY BLOCK                                                        |

|         |            |        | ctrl_rg(12) = BUSY-glitch-filter_enable introduced                                     |

| 10      | 22/07/2025 | 022    | ctrl_rg(0) =TIB_TRIG_ BUSY_BLOCK, default is '0' now                                   |

## Distribution

L2 Controller Board Rev.1, User Manual

Ref.: MST-CAM-UM-0227-DESY

Version: 10

Date: 22/07/2025

Page: 3/16

# **Table of Contents**

| 1 | IN  | TRODUCTION                                   | 4  |

|---|-----|----------------------------------------------|----|

| 2 | ТН  | E L2CB COMPONENTS                            | 4  |

| 3 | FP  | GA FIRMWARE, BLOCK DIAGRAM                   | 5  |

| 4 | L20 | CB INTERFACES                                | 6  |

|   | 4.1 | Ethernet to FPGA                             | 6  |

|   | 4.2 | L2CB to TIB                                  | 7  |

|   | 4.3 | L2CB to CTDB                                 | 8  |

| 5 | L20 | CB REGISTER ADDRESS MAP, BASE ADDRESS = 000H | 10 |

| 6 | RE  | GISTER ACCESS                                | 16 |

|   | 6.1 | Via OPCUA Server                             | 16 |

|   | 6.2 | Using a simple Register Read / Write Tool    | 16 |

CTA

Ref.: MST-CAM-UM-0227-DESY

Version: 10

L2 Controller Board Rev.1, User Manual

Date: 22/07/2025

Page: 4/16

## 1 Introduction

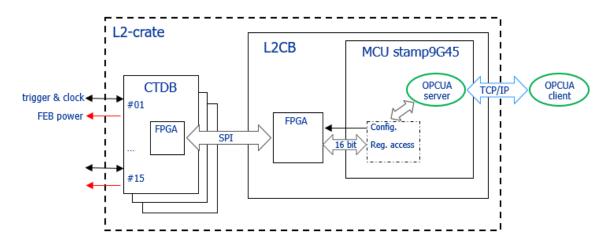

The L2CB is the central board within the L2-crate. From the users point of view, the main parts are the MCU and the FPGA. The MCU controls the FPGA. The FPGA has mainly three functions. Firstly, it receives all 265 L1 triggers and generates a L2-trigger for the TIB. Secondly it controls the 18 CTDBs, e.g. power on / off FEBs including FEB-current monitoring. Thirdly it provides the clock, PPS and L2 trigger signals to be fanned out via the CTDBs to the FEBs as L1A.

## 2 The L2CB Components

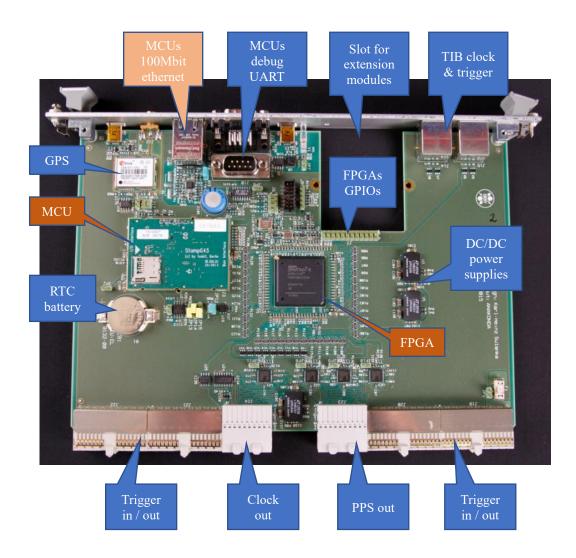

Figure 1 L2CB Components

CTA

Ref.: MST-CAM-UM-0227-DESY

Version: 10

Date: 22/07/2025

Page: 5/16

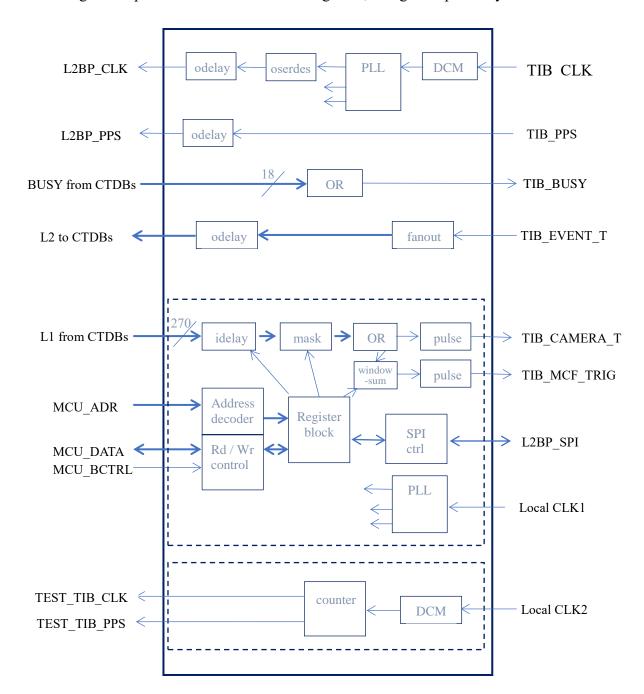

## 3 FPGA Firmware, Block Diagram

The FPGA is connected to the MCU (piggy back module) Stamp9G45 by a SRAM like bus, comprising 20 address lines, 16 data lines and control signals. Address decoder and read / write control logic is implemented to access the 18 registers, being used presently.

Figure 2 FPGA, firmware block diagram

L2 Controller Board Rev.1, User Manual

Ref.: MST-CAM-UM-0227-DESY

Version: 10

Date: 22/07/2025

Page: 6/16

## 4 L2CB Interfaces

### 4.1 Ethernet to FPGA

The microcontroller based unit Stamp9G45 is used as a 100Mbit Ethernet to FPGA-bridge. It shares a 16 bit memory bus interface with the FPGA.

For detailed information check the <u>taskit webpage</u>.

Figure 3 MCU Stamp9G45

To communicate with each of the 18 CTDBs a shared SPI bus on the L2BP is implemented. The L2CB is the bus master.

|                           | СТА                                    | Ref.: MST-CAM-UM-0227-DESY |  |

|---------------------------|----------------------------------------|----------------------------|--|

| /cta                      |                                        | Version: 10                |  |

| cherenkov telescope array | L2 Controller Board Rev.1, User Manual | Date: 22/07/2025           |  |

|                           |                                        | Page: 7/16                 |  |

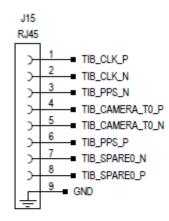

### 4.2 **L2CB to TIB**

The L2CBs upper RJ45 connector signals are described below. All signal levels are LVDS. It is assumed, that the leading edge of the 1PPS signal follows the 10MHz leading edge after 7ns. For more details check the <u>L2CB schematic</u>.

| Signal        | Remark                          |

|---------------|---------------------------------|

| TIB_CLK       | 10MHZ, TIB output               |

| TIB_PPS       | PPS, TIB output                 |

| TIB_CAMERA_T0 | L2 trigger, TIB input           |

| TIB CAMERA T1 | L2 trigger, TIB input           |

| TIB_BUSY      | FEB Ored busy-signal, TIB input |

| TIB_EVENT     | L2 trigger, TIB output          |

| TIB_SPAREx    | Reserved, TIB input             |

Figure 4 TIB signals at RJ45 connectors

|                           | СТА                                    | Ref.:   | MST-CAM-UM-0227-DESY |

|---------------------------|----------------------------------------|---------|----------------------|

| <b>cta</b>                |                                        | Version | n: 10                |

| cherenkov telescope array | L2 Controller Board Rev.1, User Manual | Date:   | 22/07/2025           |

|                           |                                        | Page:   | 8/16                 |

#### 4.3 **L2CB to CTDB**

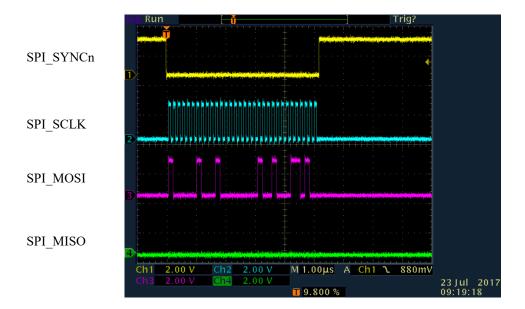

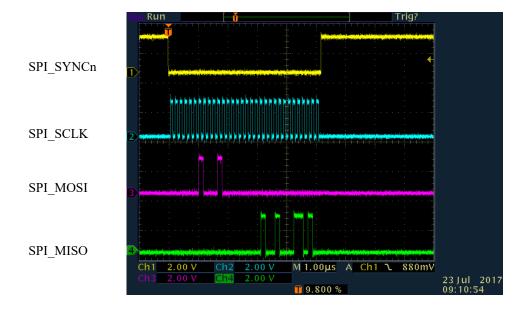

The CTDB registers are being accessed through the L2-crate backplane (L2BP). All 18 CTDBs are sharing a SPI Bus. How to initiate the SPI read or write cycle, see below, the register description.

| SPI_SCLK  | L2CB output that provides 32 clock cycles at each slow control access. The frequency of the clock it is 6.25 MHZ. The electrical standard for this signal is LVDS. Other frequencies are possible.                                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI_SYNCn | L2CB output, low during the slow control access and else high. Electrical standard for this signal is LVDS.                                                                                                                                                                                               |

| SPI_MOSI  | Master output / slave input data line. A 32-bit word is transmitted at each slow control access. Electrical standard for this signal is LVDS.  The most significant bit is transmitted first. The format of the 32-bit word is shown in table 1.                                                          |

| SPI_MISO  | Master input / slave output data line. Electrical standard for this signal is LVDS.  A 16-bit word is transmitted at each slow control access. The most significant bit is transmitted first. Active at a read access, else tristated. This line provides the information of the addressed CTDB register. |

Table 1 L2 Backplane, SPI Bus signals

| Bit range | Usage                         |

|-----------|-------------------------------|

| 31        | RD = '0', WR = '1'            |

| 30-16     | Address_140, register address |

| 15-0      | Data_150, data word           |

Table 2 Slow control 16 bit data field, Bit-15 (MSB) is sent first

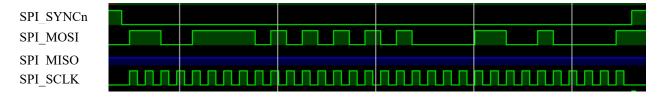

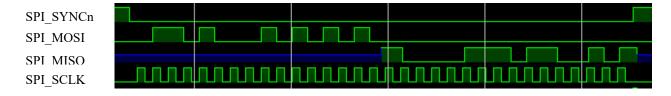

Figure 5 Example, writing data 4321h to address 4f55h

Figure 6 Example, reading data 8765h from address 68aah

| -4-                       | CTA                                    | Ref.:  | MST-CAM-UM-0227-DESY |

|---------------------------|----------------------------------------|--------|----------------------|

| <b>/cta</b>               |                                        | Versio | n: 10                |

| cherenkov telescope array | L2 Controller Board Rev.1, User Manual | Date:  | 22/07/2025           |

|                           |                                        | Page:  | 9/16                 |

Measured SPI bus cycles are illustrated below. The Bus cycle time is about 5.4 us. Higher rates can be achieved by adapting the L2CB firmware accordingly.

Figure 7 SPI write cycle of 1234h to address 20h of CTDB at slot 2

Figure 8 SPI read of 1234h from address 20h of CTDB at slot 2

L2 Controller Board Rev.1, User Manual

Ref.: MST-CAM-UM-0227-DESY

Version: 10

Date: 22/07/2025

Page: 10/16

# 5 L2CB Register Address Map, Base Address = 000h

| hex<br>addr. | Name   | Usage                                                                                               |

|--------------|--------|-----------------------------------------------------------------------------------------------------|

| 00           | CTRL   | Control register                                                                                    |

| 02           | STAT   | Status register                                                                                     |

| 04           | SPAD   | SPI Address register                                                                                |

| 06           | SPTX   | SPI Tx Data register                                                                                |

| 08           | SPRX   | SPI Rx Data register                                                                                |

| 0a           | TSTMP0 | Time stamp, bits 150                                                                                |

| 0c           | TSTMP1 | Time stamp, bits 3116                                                                               |

| 0e           | TSTMP2 | Time stamp, bits 4732                                                                               |

| 10           | TEST   | Test register, 16 bit R/W                                                                           |

| 12           | L1SEL  | L1 Trigger channel select, for masking and up delay adjust                                          |

| 14           | L1MSK  | L1 Trigger mask for channels of selected L2-crate slot                                              |

| 16           | L1DEL  | L1 trigger delay in 37ps steps, 05ns                                                                |

| 18           | MUTHR  | Muon threshold, amount of L1s, causing a Muon-trigger, *1                                           |

| 20           | MUDEL  | Programmable Muon trigger delay dealing with the time required by the 265bit adder, in steps of 5ns |

| 22           | L2DT   | L2 dead time in multiples of 5ns                                                                    |

|              |        |                                                                                                     |

|              |        |                                                                                                     |

| fe           | FREV   | Firmware Revision, bits 150                                                                         |

The registers can be accessed by the Stamp9G45 module via ethernet or the RS232 interface.

<sup>\*1</sup> available at firmware revisions 009 and later

Ref.: MST-CAM-UM-0227-DESY

Version: 10

L2 Controller Board Rev.1, User Manual Date: 22/07/2025

Page: 11/16

#### Register Description

attributeexplanationRWRead / WriteRORead Only

RWC Read / Write Clear (writing a '1' clears the bit)

#### CTRL @ address 00h, 16 bit RW, power on value = 3000h

| Bit | Attr. | Usage                                                                                                                                |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| 15  | RW    | 0 to 1 change latches a 48 bit time stamp counter, clocked by TIB_10MHz                                                              |

| 14  | RW    |                                                                                                                                      |

| 13  | RW    | MCF_ENABLE, '0' prevents the MCF-trigger being propagated to the TIB (signal TIB_SPARE1_P/N at J14-8/7), '1'= active, default is '1' |

| 12  | RW    | BUSY_GLITCH_FILTER_ENABLE, '1'= active, default is '1' *1                                                                            |

| 111 | RW    | reserved                                                                                                                             |

| 0   | RW    | TIB_TRIGGER_BUSY_BLOCK, '1'= active, default is '0' *1                                                                               |

<sup>\*1</sup> at firmware rev. 022 and higher

STAT @ address 02h, 16 bit RO, RWC, power\_on\_value = 0 (0000h)

| Bit | Attr. | Usage                              |

|-----|-------|------------------------------------|

| 0   | RO    | '1'= SPI bus cycle busy            |

| 1   | RO    | '1'= L1 delay set busy             |

| 2   | RO    | '1' = TIB is in (stuck) busy state |

| 152 | '0'   | Reserved, read value is '0'        |

Status bits to poll on the readiness of the operation.

Any write operation to the SPAD register initiates a SPI cycle to access a certain CDTB. For SPI write operations, data have to be written to the SPTX register first! Before initiating the next SPI cycle check STAT-bit\_0 (polling on readiness).

**SPAD** @ address 04h, 13 bit RW, power on value = 0 (0000h)

| Bit  | Attr. | Usage                                |

|------|-------|--------------------------------------|

| 70   | RW    | CTDB register address                |

| 128  | RW    | L2-Crate, CTDB slot number: 19, 1321 |

| 1413 | '0'   | Reserved, write '0'                  |

| 15   | RW    | '1' = Write cycle, '0' = Read cycle  |

CTA Ref.: MST-CAM-UM-0227-DESY

Version: 10

L2 Controller Board Rev.1, User Manual

Date: 22/07/2025

Page: 12/16

L2 Controller Board Rev.1, User Manual

Ref.: MST-CAM-UM-0227-DESY

Version: 10

Date: 22/07/2025

13/16 Page:

**SPTX** @ address 06h, 16 bit RW, power on value = 0 (0000h)

| Bit | Attr. | Usage                                 |

|-----|-------|---------------------------------------|

| 150 | RW    | SPI (CTDB register ) data, to be sent |

#### **SPRX** (a) address 08h, 16 bit RO, power on value = 0 (0000h)

| Bit | Attr. | Usage                              |

|-----|-------|------------------------------------|

| 150 | RO    | SPI (CTDB register ) data received |

The 0 to 1 transition of the CTRL-reg. bit 15 latches the 48 bit counter, driven by a 125MHz clock (8ns). The clock is synchronous to the TIB-10MHz clock.

### **TSTMP0** @ address 0ah, 16 bit RO, power\_on\_value = 0 (0000h)

| Bit | Attr. | Usage                                  |

|-----|-------|----------------------------------------|

| 150 | RO    | time stamp, bits 150, multiples of 8ns |

### **TSTMP1** @ address 0ch, 16 bit RO, power on value = 0 (0000h)

| Bit | Attr. | Usage                 |

|-----|-------|-----------------------|

| 150 | RO    | time stamp, bits 3116 |

### **TSTMP2** @ address 0eh, 16 bit RO, power\_on\_value = 0 (0000h)

| Bit | Attr. | Usage                 |

|-----|-------|-----------------------|

| 150 | RO    | time stamp, bits 4732 |

#### **TEST** @ address 10h, 16 bit RW, power on value = 0 (0000h)

| Bit | Attr. | Usage                                                   |

|-----|-------|---------------------------------------------------------|

| 150 | RW    | read / write test register, no additional functionality |

L2 Controller Board Rev.1, User Manual

Ref.: MST-CAM-UM-0227-DESY

Version: 10

Date: 22/07/2025

Page: 14/16

L1SEL @ address 12h, 16 bit RW, power on value = 0 (0000h)

| Bit | Attr. | Usage                                                |

|-----|-------|------------------------------------------------------|

| 30  | RW    | CTDB channel number of selected slot, valid are: 115 |

| 84  | RW    | L2-crate slot number, valid are: 19, 1321            |

| 159 | RO    | unused, read value is '0'                            |

After power on, all L1s are blocked. Write a '1' to the selected L1MSK bit for enabling the dedicated L1 signal.

### **L1MSK** @ address 14h, 16 bit RW, power\_on\_value = 0 (0000h)

| Bit | Attr. | Usage                                                                                                                                                                |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | RO    | unused, read value is '0'                                                                                                                                            |

| 151 | RW    | trigger mask for the selected (L1SEL reg.) slot, each channel has its own select bit, valid are 0000hfffeh, '0' means L1-trigger of the selected channel is not used |

Before changing the L1 delay of a particular channel, check the STAT-bit\_1 (polling on readiness). The delay for other channels can be set immediately. Note, the readiness for a particular channel requires the occurrence of several L1 signals.

#### **L1DEL** @ address 16h, 8 bit RW, power on value = 0 (0000h)

| Bit | Attr. | Usage                                                                            |

|-----|-------|----------------------------------------------------------------------------------|

| 70  | RW    | L1 delay of selected (by L1SEL reg.) trigger channel, usable range 0128 (x 37ps) |

| 158 | RO    | 00h                                                                              |

#### MUTHR @ address 18h, 9 bit RW, power on value = 14h,\*1

| Bit | Attr. | Usage                                                                                                                  |

|-----|-------|------------------------------------------------------------------------------------------------------------------------|

| 80  | RW    | Muon trigger threshold, amount of simultaneous L1s within the programmable (MUDEL) trigger window, default is 20 (dec) |

| 159 | RO    | 00h                                                                                                                    |

<sup>\*1</sup> available at firmware revisions 013 and later

### MUDEL @ address 20h, 4 bit RW, power\_on\_value = 0ah,\*2

| Bit | Attr. | Usage                                                                                           |

|-----|-------|-------------------------------------------------------------------------------------------------|

| 30  | RW    | Muon trigger window in multiples of 5ns after the L1-up (TIB_CAMERA_T) LH-edge, default is 50ns |

| 154 | RO    | 00h                                                                                             |

<sup>\*2</sup> available at firmware revisions 014 and later

Ref.: MST-CAM-UM-0227-DESY

Version: 10

L2 Controller Board Rev.1, User Manual

Date: 22/07/2025

Page: 15/16

## L1DT @ address 22h, 8 bit RW, power\_on\_value = 0000h,\*3

| Bit | Attr. | Usage                                                     |

|-----|-------|-----------------------------------------------------------|

| 70  | RW    | L1-up trigger (TIB_CAMERA_Tx) dead time, multiples of 5ns |

| 168 | RO    | 00h                                                       |

<sup>\*3</sup> available at firmware revisions 016 and later, at 00h the dead time is 15ns

### FREV @ address fe, 16 bit RO

| Bit | Attr. | Usage                                   |

|-----|-------|-----------------------------------------|

| 150 | RO    | read back of the L2CB firmware revision |

CTA

Ref.: MST-CAM-UM-0227-DESY

Version: 10

L2 Controller Board Rev.1, User Manual

Date: 22/07/2025

Page: 16/16

## 6 Register Access

#### 6.1 Via OPCUA Server

An OPCUA server, developed by David Melkumyan, is running on the MCU. For details, check MST-CAM-TN-0481-DESY.

Figure 9 Register access via OPCUA server

## 6.2 Using a simple Register Read / Write Tool

A simple register access tool is implemented on the MCU as well. Esp. for debugging it can be very useful. Instead of the ethernet connection one can also use the MCUs debug RS232 / UART port with the following settings: 115200baud, 1,8,1,no parity, no flow control .

login:root password:taskit

Useful commands are:

ls /opt/cta/bin

cta ctrl -h // CTDB access

smcrw -h // L2CB register access